# Wireless CPU Q24 Series Customer Design Guideline

Revision: 002 Date: September 2006

Operating Systems Plug-Ins Integrated Development Environments Wireless CPUs Services

## **Customer Design Guideline**

Reference: WM\_PRJ\_024NG\_CDG\_002 Revision: 002 Date: September 2006

Powered by the Open AT® Software Suite

wavecom<sup>®</sup> confidential ©

Page: 1 / 90

**Cautions**

This platform contains a modular transmitter. This device is used for wireless applications. Note that all electronics parts and elements are ESD sensitive.

Information provided herein by WAVECOM is accurate and reliable. However, no responsibility is assumed for its use and any of such WAVECOM information is herein provided "as is" without any warranty of any kind, whether express or implied.

## **Trademarks**

(R), WAVECOM<sup>®</sup>, WISMO<sup>®</sup>, Open AT<sup>®</sup> and certain other trademarks and logos appearing on this document, are filed or registered trademarks of Wavecom S.A. in France or in other countries. All other company and/or product names mentioned may be filed or registered trademarks of their respective owners.

## Copyright

This manual is copyrighted by WAVECOM with all rights reserved. No part of this manual may be reproduced in any form without the prior written permission of WAVECOM. No patent liability is assumed with respect to the use of their respective owners.

### wavecom<sup>®</sup> confidential ©

Page: 2 / 90

## Web Site Support

General information about Wavecom and its range of products: www.wavecom.com

Specific support is available for the Q24 Classic, Plus, Extended and Auto Wireless CPU: <a href="http://www.wavecom.com/Q24Classic">www.wavecom.com/Q24Classic</a>,

www.wavecom.com/Q24Plus,

www.wavecom.com/Q24Extended,

www.wavecom.com/Q24Auto

Carrier/Operator approvals: www.wavecom.com/approvals

Open AT® Introduction: www.wavecom.com/OpenAT

Developer support for software and hardware: www.wavecom.com/forum

wavecom<sup>®</sup> confidential ©

Page: 3 / 90

**Overview**

This document gives recommendations and general guidelines to help design a product using the Wireless CPU Q24 Series.

The recommendations include:

- Design rules and typical implementation examples,

- Mechanical constraints,

- PCB layout recommendations,

- Test and download recommendations.

The Wireless CPU Q24 Series is available in four different GSM/GPRS Class 10 quadband versions:

• **Q24 Classic**: **EGSM 900/1800/850/1900** MHz version with **32** Mb of Flash memory and **16** Mb of PSRAM (**32/16**), T° range **[-20°C / +55°C]**.

• **Q24 Plus: EGSM/GPRS 900/1800/850/1900** MHz version with **32** Mb of Flash memory and **16** Mb of PSRAM (**32/16**), T° range **[-20°C / +55°C]**.

• **Q24 Extended**: **EGSM/GPRS 900/1800/850/1900** MHz version with **32** Mb of Flash memory and **4** Mb of SRAM (**32/4**), extended T° range.

• **Q24 Automotive: EGSM/GPRS 900/1800/850/1900** MHz version with **32** Mb of Flash memory and **4** Mb of PSRAM (**32/4**), extended T° range.

This version is dedicated to automotive applications.

For further information about the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

## For detailed software programming guides, refer to the documents shown in the "Reference documents" section.

Open AT® Software Suites allow developers to natively execute ANSI C software programs directly on the Wireless CPU.

### wavecom<sup>®</sup> confidential ©

## **Document History**

| Revision | Date                | List of revisions              |  |

|----------|---------------------|--------------------------------|--|

| 001      | May 2006            | Creation (Preliminary version) |  |

| 002      | September -<br>2006 | First update                   |  |

wavecom<sup>®</sup> confidential ©

Page: 5 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

September 2006

## Contents

| Cauti                                                | ons2                                                                                        |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| Trade                                                | Trademarks2                                                                                 |  |  |  |

| Сору                                                 | right2                                                                                      |  |  |  |

| Web                                                  | Site Support3                                                                               |  |  |  |

| Over                                                 | /iew4                                                                                       |  |  |  |

| Docu                                                 | ment History5                                                                               |  |  |  |

| Conte                                                | ents6                                                                                       |  |  |  |

| Table                                                | of Figures10                                                                                |  |  |  |

| 1                                                    | References12                                                                                |  |  |  |

| 1.1<br>1.1<br>1.1                                    |                                                                                             |  |  |  |

| 1.2                                                  | Abbreviations                                                                               |  |  |  |

| 2                                                    | General Description17                                                                       |  |  |  |

| 2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1 | .2GSM/GPRS Features17.3Interfaces17.4External RF Connection Interfaces18.5SIM CARD Holder18 |  |  |  |

| 2.2                                                  | Functional Architecture                                                                     |  |  |  |

| 3                                                    | Power Supply Recommendations20                                                              |  |  |  |

| 3.1                                                  | Ground Connections Recommendations                                                          |  |  |  |

## wavecom<sup>®</sup> confidential ©

Page: 6 / 90

| 3.2                                           | Pow                  | er Supply Generalities                                                                                                                                                                              | 21                   |

|-----------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.3                                           | Volta                | age Versus Distance                                                                                                                                                                                 | 21                   |

| 3.4                                           | Volta                | age Versus Time                                                                                                                                                                                     | 23                   |

| 3.5<br>3.5<br>3.5<br>3.5                      | .1<br>.2             | gn Recommendation<br>Power Supply Selection<br>Design of the Supply Track<br>Decoupling capacitors                                                                                                  | 24<br>25             |

| 4                                             | Pow                  | er Consumption                                                                                                                                                                                      | 28                   |

| 5                                             | Inte                 | rfaces                                                                                                                                                                                              | 31                   |

| 5.1                                           | Digit                | al I/O and Peripheral Implementation                                                                                                                                                                | 31                   |

| 5.2<br>5.2<br>5.2<br>5.2                      | .1<br>.2             | al Interface<br>SPI Bus<br>I <sup>2</sup> C Bus<br>SPI and I <sup>2</sup> C Bus Implementation                                                                                                      | 31<br>32             |

| 5.3                                           | Keyb                 | ooard Interface                                                                                                                                                                                     | 34                   |

| 5.4<br>5.4<br>5.4                             | .1                   | n Serial Link (UART1)<br>General Description<br>Design Recommendation                                                                                                                               | 35                   |

| 5.5<br>5.5<br>5.5                             | .1                   | liary Serial Link (UART2)<br>General Description<br>Design Recommendation                                                                                                                           | 38                   |

| 5.6<br>5.6<br>5.6<br>5.6                      | .1<br>.2             | Interface<br>General Description<br>Design Recommendation<br>Wireless CPU SIM CARD Holder                                                                                                           | 39<br>39             |

| 5.7                                           | Anal                 | og to Digital Converter (ADC)                                                                                                                                                                       | 46                   |

| 5.8<br>5.8<br>5.8<br>5.8<br>5.8<br>5.8<br>5.8 | .1<br>.2<br>.3<br>.4 | o Interface<br>Recommended Microphone Characteristics<br>Recommended Speaker Characteristics<br>Recommended Filtering Components<br>Audio track and PCB Layout Recommendation<br>Microphone Inputs. | 47<br>48<br>48<br>50 |

| 5.9<br>5.9<br>5.9                             | .1                   | er Output<br>General Description<br>Design Recommendation                                                                                                                                           | 56                   |

| 5.1                                           |                      | ery Charging Interface<br>General Description<br>Design Recommendation                                                                                                                              | 57                   |

| 5.11                                          | ON /                 | ~OFF                                                                                                                                                                                                | 60                   |

## wavecom<sup>®</sup> confidential ©

### Page: 7 / 90

| 12        | Firm                     | ware Upgrade                                                                | 82 |

|-----------|--------------------------|-----------------------------------------------------------------------------|----|

| 11        | Deb                      | ug and Testability                                                          | 81 |

| 10        | РСВ                      | Layout in General                                                           | 80 |

| 9.2       | I/O C                    | Circuit Diagram                                                             | 79 |

| 9.1       | Gene                     | eral Purpose Connector Pin-out Description                                  | 75 |

| 9         | Tecl                     | nnical Specifications                                                       | 75 |

| 8         | EMC                      | Recommendations                                                             | 74 |

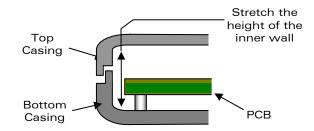

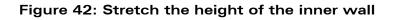

| 7.3       | Stret                    | ch Cabinet Wall                                                             | 73 |

| 7.2       |                          | Layout against ESD                                                          |    |

| 7.1       |                          | Consideration                                                               |    |

|           | .2.2                     | RF connection                                                               | 69 |

| 6.2<br>6  | Ante<br>.2.1             | nna Implementation<br>Recommendations                                       |    |

| 6.1       | Ante                     | enna Characteristics Recommendation                                         | 68 |

| 6         | Radi                     | io Design                                                                   | 68 |

| 5         | 8 Real<br>.16.1<br>.16.2 | Time Clock Supply (VCC_RTC)<br>General Description<br>Design Recommendation | 66 |

| 5.15<br>5 | 5 VCC<br>.15.1           | Output<br>General Description                                               | 65 |

| 5         | Exte<br>.14.1<br>.14.2   | rnal Interrupt (~INTR)<br>General Description<br>Design Recommendation      | 65 |

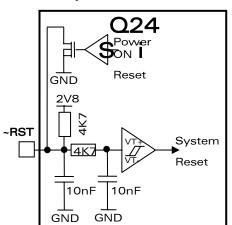

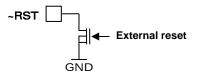

| 5         | 3 Rese<br>.13.1<br>.13.2 | et Signal (~RST)<br>General Description<br>Design Recommendation            | 63 |

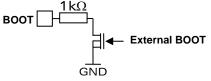

| 5         | 2 BOO<br>.12.1<br>.12.2  | T (optional)<br>General Description<br>Design Recommendation                | 62 |

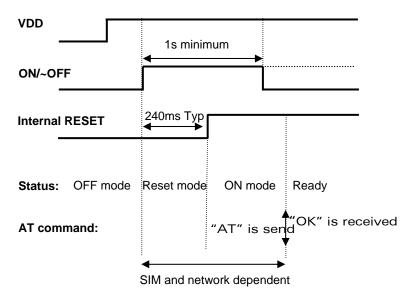

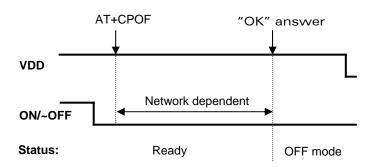

| 5         | .11.1<br>.11.2<br>.11.3  | General Description<br>Operating Sequences<br>Power OFF                     | 61 |

## wavecom<sup>®</sup> confidential ©

Page: 8 / 90

| 12.               | Recommendations<br>1.1 Nominal Upgrade Procedure<br>1.2 Backup Procedure                              | 82             |  |

|-------------------|-------------------------------------------------------------------------------------------------------|----------------|--|

| 13                | Product Manufacturing Design Rules                                                                    | 84             |  |

| 13.1              | Recommendation for Lead Free Soldering                                                                | 84             |  |

| 14                | Mechanical Specifications                                                                             | 85             |  |

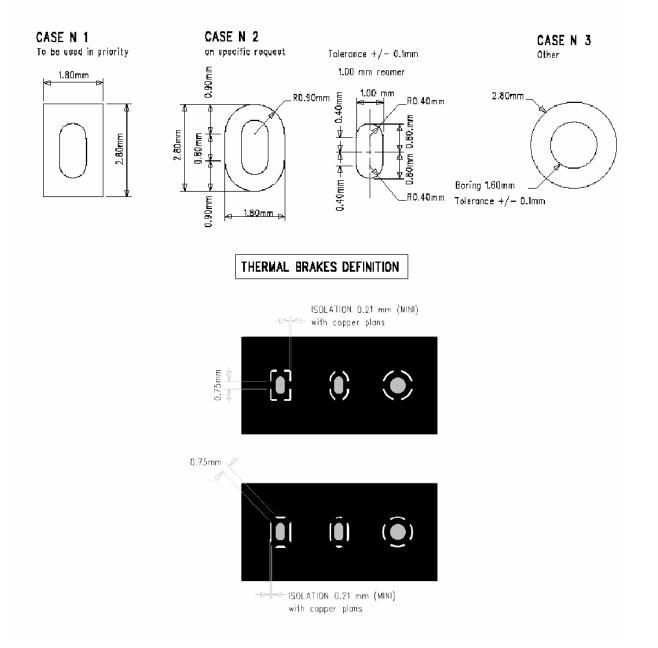

| 14.1              | Pad Design                                                                                            | 87             |  |

| 14.2              | Part References and Suppliers                                                                         | 88             |  |

| 14.3              | General Purpose Connector                                                                             | 88             |  |

| 14.4              | SIM Card Reader                                                                                       |                |  |

| 14.5              | Microphone                                                                                            | 88             |  |

| 14.6              | Speaker                                                                                               | 89             |  |

| 14.<br>14.<br>14. | Antenna Connections7.1Antenna Pad7.2IMP Connector (RF board to board)7.3UFL Connector7.4MMS Connector | 89<br>89<br>89 |  |

| 14.8              | GSM Antenna                                                                                           | 90             |  |

wavecom<sup>®</sup> confidential ©

wavecom

Make it wireless

Page: 9 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

September 2006

## **Table of Figures**

| Figure 1: Functional architecture1                             | 19 |

|----------------------------------------------------------------|----|

| Figure 2: Q24 Series and ground connections2                   | 20 |

| Figure 3: Shielding legs connections2                          | 20 |

| Figure 4: Voltage drop versus distance2                        | 21 |

| Figure 5: Typical Li-Ion battery connection2                   | 22 |

| Figure 6: Voltage drop versus time2                            | 23 |

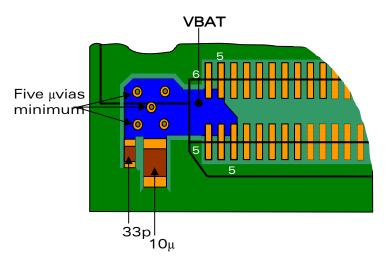

| Figure 7: VBATT supply track and PCB layout2                   | 27 |

| Figure 8: VBATT and decoupling capacitors2                     | 27 |

| Figure 9: Example of Keyboard implementation                   | 34 |

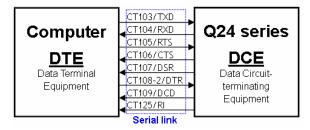

| Figure 10: UART1 Serial Link signals                           | 35 |

| Figure 11: Typical UART1 and host connection                   | 36 |

| Figure 12: Example of RS232 level shifter implementation       | 38 |

| Figure 13: UART2 Serial Link signals                           | 39 |

| Figure 14: Example of SIM Socket implementation4               | 10 |

| Figure 15: Example of SIM Socket and PCB layout4               | 11 |

| Figure 16: SIM signals and layout4                             | 12 |

| Figure 17: SIM CARD holder constraints4                        | 14 |

| Figure 18: Example of ADC input implementation4                | 17 |

| Figure 19: Microphone4                                         | 18 |

| Figure 20: Audio track design                                  | 50 |

| Figure 21: MIC1 inputs and single-ended connection             | 51 |

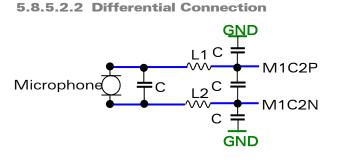

| Figure 22: MIC1 inputs and differential connection             | 52 |

| Figure 23: MIC2 inputs and differential connection             | 54 |

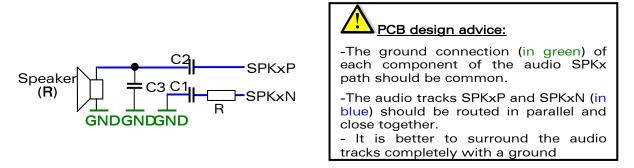

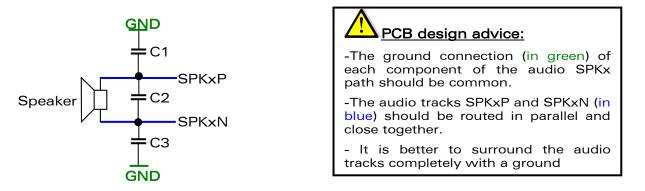

| Figure 24: Example of single-ended mode speaker implementation | 55 |

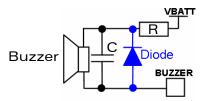

| Figure 25: Buzzer connection                                   | 57 |

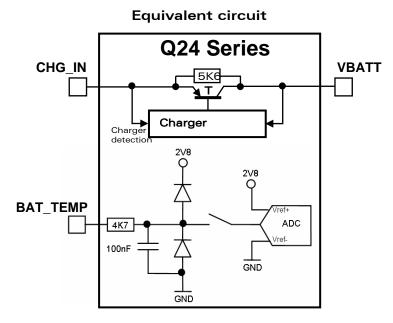

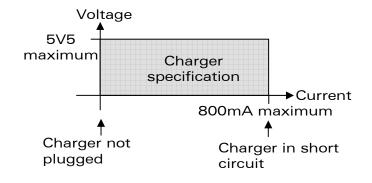

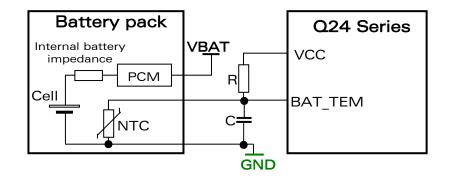

| Figure 26: Charger recommendation                              | 59 |

| Figure 27: Example of battery implementation                   | 59 |

| Figure 28: Power-ON sequence diagram6                          | 31 |

| Figure 29: Power-OFF sequence diagram6                         | 32 |

| Figure 30: BOOT pin connection6                                | 33 |

### wavecom<sup>®</sup> confidential ©

### Page: 10 / 90

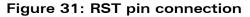

| Figure 31: RST pin connection                             | 64 |

|-----------------------------------------------------------|----|

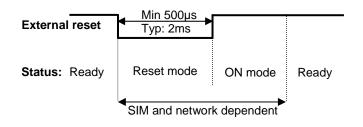

| Figure 32: Reset sequence diagram                         | 65 |

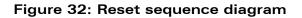

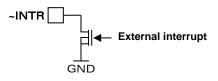

| Figure 33: INTR pin connection                            | 65 |

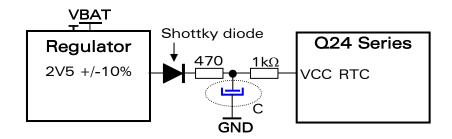

| Figure 34: RTC Supplied by a capacitor or super capacitor | 66 |

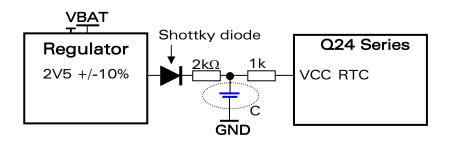

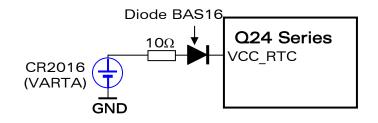

| Figure 35: RTC Supplied by a battery cell                 | 67 |

| Figure 36: RTC supplied by a non-rechargeable battery     | 67 |

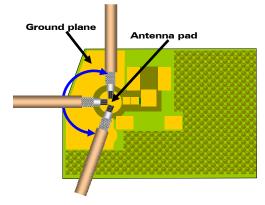

| Figure 37: Antenna connection                             | 69 |

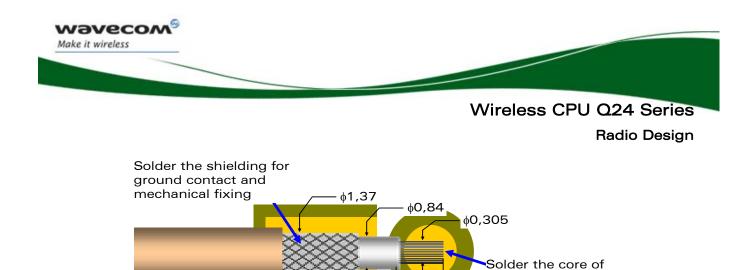

| Figure 38: Antenna cable preparation                      | 70 |

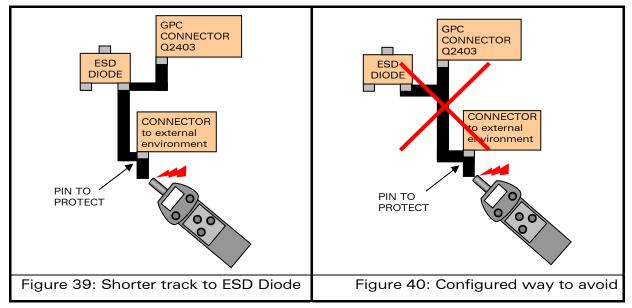

| Figure 39: Shorter track to ESD Diode                     | 72 |

| Figure 40: Configured way to avoid                        | 72 |

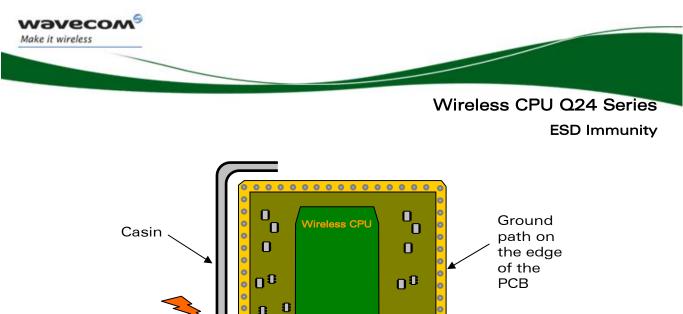

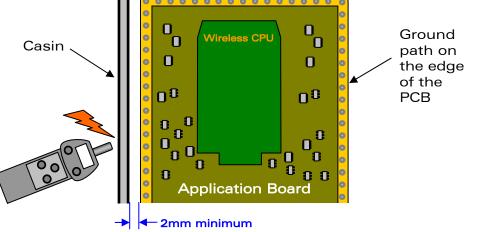

| Figure 41: Top and Bottom Layers with ground plane        | 73 |

| Figure 42: Stretch the height of the inner wall           | 73 |

| Figure 43: Stretch the height of the inner wall           | 73 |

| Figure 44: Wireless CPU pin position (bottom view)        | 75 |

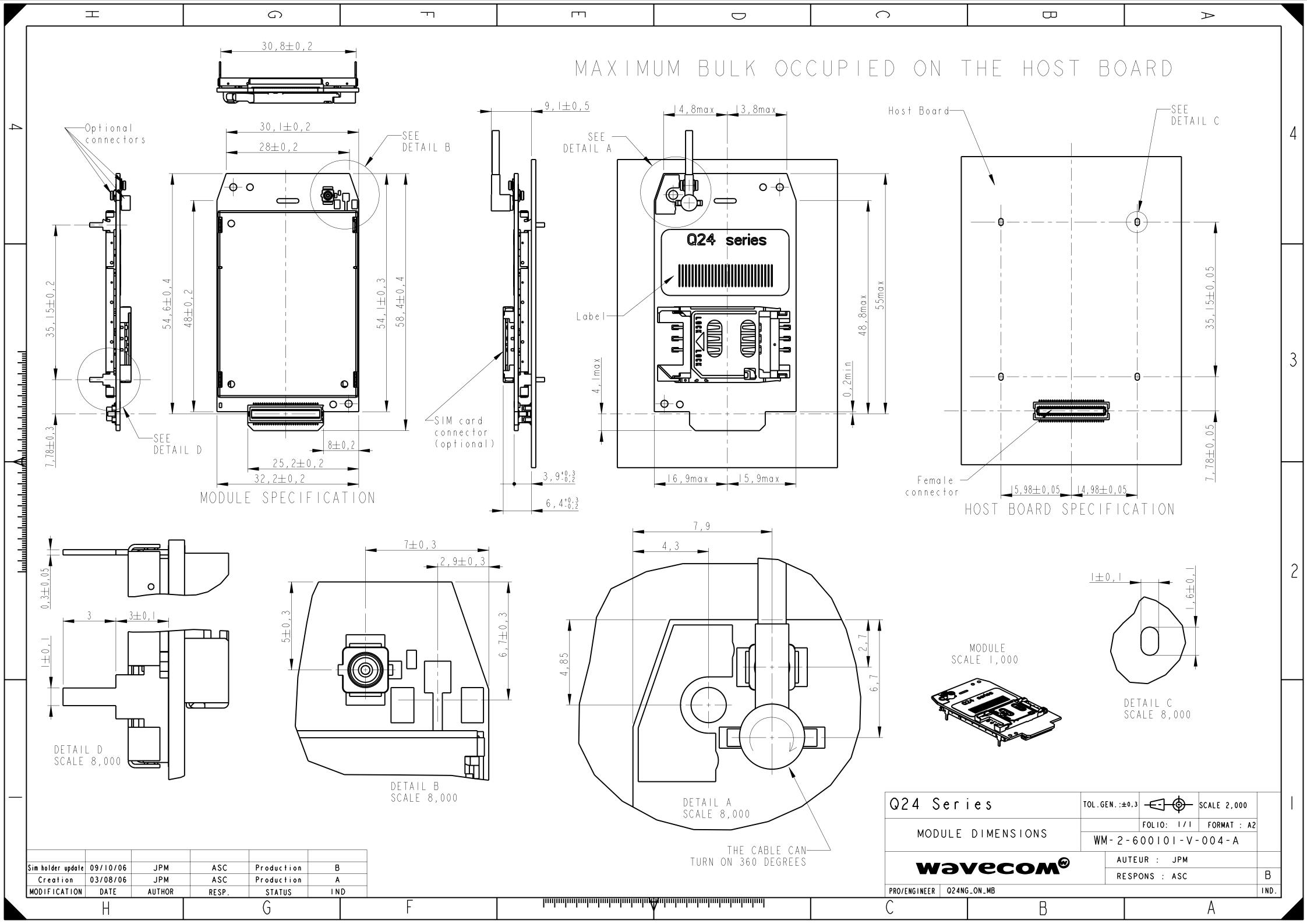

| Figure 45: Maximum area occupied on the application board |    |

| Figure 46: Pad design                                     | 87 |

wavecom<sup>®</sup> confidential ©

Page: 11 / 90

## **1** References

### **1.1 Reference Documents**

For more details, several reference documents may be consulted. The Wavecom reference documents are provided in the Wavecom documents package contrary to the general reference documents, which are not Wavecom owned.

### **1.1.1 Wavecom Reference Documents**

- [1] Automotive Environmental Control Plan for Wireless CPU Q24 Series WM\_PRJ\_Q24NG\_DCP\_001

- [2] Environmental Control Plan for Wireless CPU Q24 Series WM\_PRJ\_Q24NG\_DCP\_002

- [3] Wireless CPU Q24 Series Product Technical Specification WM\_PRJ\_Q24NG\_PTS\_002

- [4] Wireless CPU Q24 Series Process Customer Guidelines WM\_PRJ\_Q24NG\_PTS\_003

- [5] AT Commands Interface Guide for OS 6.57 WM\_ASW\_OAT\_UGD\_0044

- [6] AT Commands Interface Guide (Bluetooth) WM\_ASW\_BLU\_UGD\_001

- [7] ADL User Guide for Open ATA® V.3.12 WM\_ASW\_OAT\_UGD\_006

### **1.1.2 General Reference Documents**

- [8] "I<sup>2</sup>C Bus Specification", Version 2.0, Philips Semiconductor 1998

- [9] ISO 7816-3 Standard

wavecom<sup>®</sup> confidential ©

Page: 12 / 90

| Abbreviation | Definition                              |

|--------------|-----------------------------------------|

| AC           | Alternating Current                     |

| ADC          | Analog to Digital Converter             |

| A/D          | Analog to Digital conversion            |

| AF           | Audio-Frequency                         |

| AT           | ATtention (prefix for modem commands)   |

| AUX          | AUXiliary                               |

| CAN          | Controller Area Network                 |

| СВ           | Cell Broadcast                          |

| CEP          | Circular Error Probable                 |

| CLK          | CLocK                                   |

| CMOS         | Complementary Metal Oxide Semiconductor |

| CS           | Coding Scheme                           |

| CTS          | Clear To Send                           |

| DAC          | Digital to Analog Converter             |

| dB           | Decibel                                 |

| DC           | Direct Current                          |

| DCD          | Data Carrier Detect                     |

| DCE          | Data Communication Equipment            |

| DCS          | Digital Cellular System                 |

| DR           | Dynamic Range                           |

| DSR          | Data Set Ready                          |

| DTE          | Data Terminal Equipment                 |

| DTR          | Data Terminal Ready                     |

| EFR          | Enhanced Full Rate                      |

| E-GSM        | Extended GSM                            |

| EMC          | ElectroMagnetic Compatibility           |

| EMI          | ElectroMagnetic Interference            |

| EMS          | Enhanced Message Service                |

|              |                                         |

## wavecom<sup>®</sup> confidential ©

Page: 13 / 90

| Abbreviation | Definition                                               |

|--------------|----------------------------------------------------------|

| EN           | ENable                                                   |

| ESD          | ElectroStatic Discharges                                 |

| FIFO         | First In Fi <b>rst O</b> ut                              |

| FR           | Full Rate                                                |

| FTA          | Full Type Approval                                       |

| GND          | GrouND                                                   |

| GPI          | General Purpose Input                                    |

| GPC          | General Purpose Connector                                |

| GPIO         | General Purpose Input Output                             |

| GPO          | General Purpose Output                                   |

| GPRS         | General Packet Radio Service                             |

| GPS          | Global Positioning System                                |

| GSM          | Global System for Mobile communications                  |

| HR           | Half Rate                                                |

| I/O          | Input / <b>O</b> utput                                   |

| LED          | Light Emitting Diode                                     |

| LNA          | Low Noise Amplifier                                      |

| MAX          | MAXimum                                                  |

| MIC          | MICrophone                                               |

| MIN          | MINimum                                                  |

| MMS          | Multimedia Message Service                               |

| MO           | Mobile Originated                                        |

| MT           | Mobile Terminated                                        |

| na           | Not Applicable                                           |

| NF           | Noise Factor                                             |

| NMEA         | National Marine Electronics Association                  |

| NOM          | NOMinal                                                  |

| NTC          | Négative Temperature Coefficient                         |

| PA           | Power Amplifier                                          |

| Pa           | <b>Pa</b> scal (for speaker sound pressure measurements) |

| PBCCH        | Packet Broadcast Control CHannel                         |

## wavecom<sup>®</sup> confidential ©

Page: 14 / 90

| Abbreviation | Definition                                       |

|--------------|--------------------------------------------------|

| PC           | Personal Computer                                |

| PCB          | Printed Circuit Board                            |

| PDA          | Personal Digital Assistant                       |

| PFM          | Power Frequency Modulation                       |

| PSM          | Phase Shift Modulation                           |

| PWM          | Pulse Width Modulation                           |

| RAM          | Random Access Memory                             |

| RF           | Radio Frequency                                  |

| RFI          | Radio Frequency Interference                     |

| RHCP         | Right Hand Circular Polarization                 |

| RI           | Ring Indicator                                   |

| RST          | ReSeT                                            |

| RTC          | Real Time Clock                                  |

| RTCM         | Radio Technical Commission for Maritime services |

| RTS          | Request To Send                                  |

| RX           | Receive                                          |

| SCL          | Serial CLock                                     |

| SDA          | Serial DAta                                      |

| SIM          | Subscriber Identification Wireless CPU           |

| SMS          | Short Message Service                            |

| SPI          | Serial Peripheral Interface                      |

| SPL          | Sound Pressure Level                             |

| SPK          | SPeaKer                                          |

| SRAM         | Static RAM                                       |

| ТВС          | To Be Confirmed                                  |

| TDMA         | Time Division Multiple Access                    |

| ТР           | Test Point                                       |

| TVS          | Transient Voltage Suppressor                     |

| ТХ           | Transmit                                         |

| TYP          | TYPical                                          |

| UART         | Universal Asynchronous Receiver-Transmitter      |

|              |                                                  |

## wavecom<sup>®</sup> confidential ©

Page: 15 / 90

## Wireless CPU Q24 Series References

| Abbreviation | Definition |

|--------------|------------|

|              |            |

- USB Universal Serial Bus

- USSD Unstructured Supplementary Services Data

- VSWR Voltage Standing Wave Ratio

wavecom<sup>®</sup> confidential ©

Page: 16 / 90

**General Description**

## **2 General Description**

## **2.1 General Information**

The Wireless CPU Q24 Series are self-contained EGSM/GPRS 900/1800 and 850/1900 quad-band Wireless CPUs with the following characteristics.

### Note:

Only the Q24 classic is limited to GSM (GPRS not supported).

### 2.1.1 Overall Dimensions

Completely shielded:

- Length: 58.4 mm

- Width: 32.2 mm

- Thickness: 3.9 mm

- Excluding shielding legs

- 6.2 mm for Q24 Automotive which offers a MMS or UFL connector on the top side

- Weight:<11 g (12g for Q24 Automotive)

### 2.1.2 GSM/GPRS Features

- 2-Watt EGSM 900/GSM 850 radio section running under 3.6 volts

- 1-Watt GSM1800/1900 radio section running under 3.6 Volts

- Hardware GSM/GPRS class 10 capable (except the Wireless CPU Q24 Classic)

### 2.1.3 Interfaces

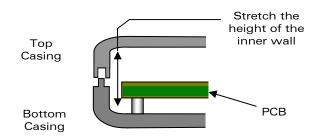

- Complete interfacing is through a 60-pin connector:

- o SPI and I<sup>2</sup>C bus interfaces

- o Keyboard interfaces

- o Two serial links interfaces (UART1 and UART2)

- o 3V/1.8V SIM interface

- o GPIOs

- o Activity status indication interface

- o Analog to digital converter

- o Analog audio

- o Buzzer interface

- o Battery charging interface

- o External interrupt

- o Power supply interface

### wavecom<sup>®</sup> confidential ©

#### Page: 17 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

#### WM\_PRJ\_024NG\_CDG\_002-002

General Description

- o Back-up battery interface

- Optional SIM Card holder

### 2.1.4 External RF Connection Interfaces

The Wireless CPU Q24 Series are available with different external RF connection configurations:

| Product<br>reference | UFL         | UFL or MMS | Antenna pad | IMP         |

|----------------------|-------------|------------|-------------|-------------|

| Position             | bottom side | top side   | top side    | bottom side |

| Q24 Classic          | Х           |            | Х           | Х           |

| Q24 Plus             | Х           |            | Х           | Х           |

| Q24 Extended         | Х           |            | Х           | Х           |

| Q24<br>Automotive    |             | Х          | Х           | Х           |

### 2.1.5 SIM CARD Holder

The Wireless CPU Q24 Series are available with a SIM CARD holder on the TOP:

|                      | SIM interface location |                     |  |

|----------------------|------------------------|---------------------|--|

| Product<br>reference | 60-pin connector       | Optional SIM holder |  |

| Q24 Classic          | Х                      | Х                   |  |

| Q24 Plus             | Х                      | Х                   |  |

| Q24 Extended         | Х                      |                     |  |

| Q24<br>Automotive    | Х                      |                     |  |

- The Wireless CPU Q24 Series does not allow two SIM Cards to be connected at the same time.

- If a Wireless CPU Q24 Plus or Extended is used with a SIM CARD holder at the top, It is <u>mandatory</u> to avoid the SIM interface through the 60-pin General Purpose Connector (GPC).

### 2.1.6 Green Policy

The Wireless CPU Q24 Series are compliant with RoHS (Restriction of Hazardous Substances in Electrical and Electronic Equipment). Directive 2002/95/EC, which sets limits for the use of certain restricted hazardous substances.

This directive states that "from 1st July 2006, new electrical and electronic equipment put on the market does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE)".

### wavecom<sup>®</sup> confidential ©

Page: 18 / 90

### **General Description**

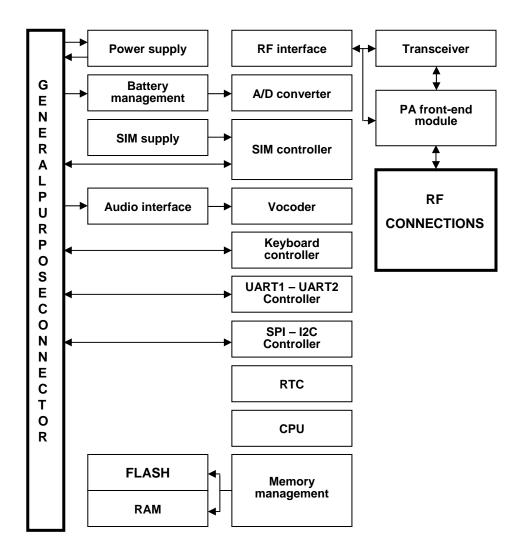

## **2.2 Functional Architecture**

The global architecture of the Wireless CPU Q24 Series is shown below:

Figure 1: Functional architecture

wavecom<sup>®</sup> confidential ©

Page: 19 / 90

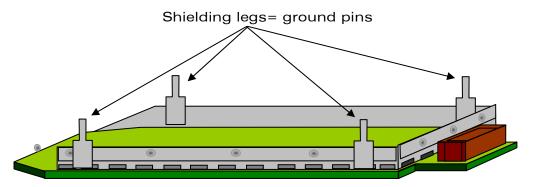

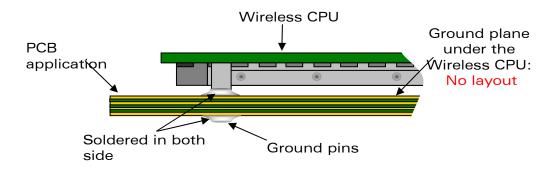

## **3.1 Ground Connections Recommendations**

The ground connections of the Wireless CPU Q24 Series are made through the four legs of the shielding.

Figure 2: Q24 Series and ground connections

- A complete ground plane must connect the four legs of the Wireless CPU.

- Connections between other ground planes must be made either with vias or  $_{\mbox{$\mu$}}\mbox{vias}.$

- The ground pins must be soldered on both sides of the PCB. This helps speed up the heat dissipation process.

To avoid coupling effect with radiated noise, it is recommended to avoid layout at the top layer of the application located under the Wireless CPU.

Figure 3: Shielding legs connections

### wavecom<sup>®</sup> confidential ©

Page: 20 / 90

## **3.2 Power Supply Generalities**

The power supply is one of the key factors in the design of a GSM terminal.

The VBATT voltage limits must be at any time: **3.2V <VBATT < 4.5V**

The worst condition is during the burst period transmission, when current consumption is at its highest. During this period, the VBATT voltage is minimum:

- The output voltage of the power supply drops.

- Voltage drop is present between the power supply output and the Wireless CPU supply pins (VBATT).

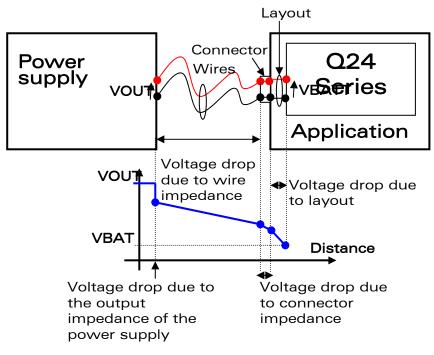

## **3.3 Voltage Versus Distance**

Depending on the distance between the power supply and the Wireless CPU, behavior is as follows:

Figure 4: Voltage drop versus distance

For further information about the power supply of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

## wavecom<sup>®</sup> confidential ©

Page: 21 / 90

- The total impedance (power supply output impedance+ wires+ connectors+ layout) must be below  $150m\Omega$ .

- The design of the supply path between the Wireless CPU and the power supply must take into account the forward and return paths.

### Example:

Using a Li-Ion battery to supply a Wireless CPU, the total impedance of the supply track must be divided as follows:

- Cell impedance ≅70 mΩ

- PCM impedance ≅50 mΩ

- Battery connector  $\cong 20 \text{ m}\Omega$

- PCB supplying track  $\cong$ 10 m $\Omega$  (forward and return path)

**Totally:** Cell +PCM + connector+ supplying track  $\cong$  150m $\Omega$

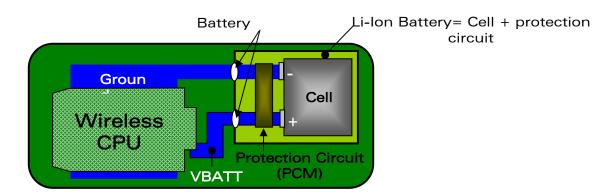

Figure 5: Typical Li-Ion battery connection

### wavecom<sup>®</sup> confidential ©

Page: 22 / 90

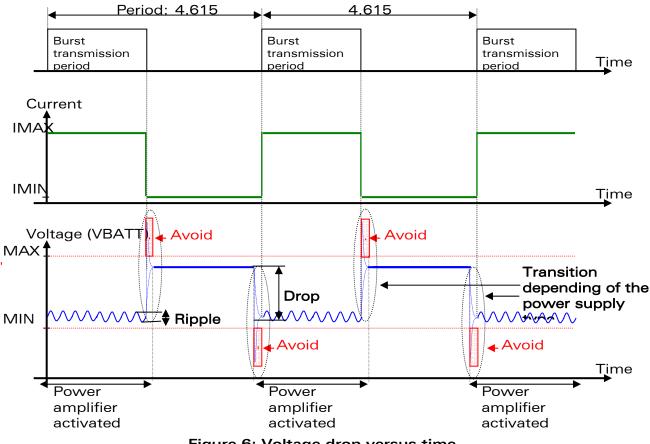

## **3.4 Voltage Versus Time**

According to time, the voltage supplying a GSM terminal varies as follows:

Figure 6: Voltage drop versus time

### Note:

The burst transmission period depends on the transmitted burst:

577µs for one transmit burst and 1154 µs for 2 transmitted bursts (GPRS class 10)

## Caution:

The waveform of the voltage may affect the performance of the Wireless CPU:

- If the drop is too high, the VBATT voltage reaches the minimum admissible limit (VBATT  $_{\rm MIN}{=}3.2{\rm V}).$

- If VBATT<VBATT <sub>MIN</sub> at any time, the Wireless CPU powers OFF automatically.

## wavecom<sup>®</sup> confidential ©

### Page: 23 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

#### WM\_PRJ\_Q24NG\_CDG\_002-002

Wireless CPU Q24 Series Power Supply Recommendations

• If the power supply time response is too long, transients may appear.

These transients may make the voltage:

- higher than the maximum admissible limit (VBATT<sub>MAX</sub>=4.5V)

- lower than the minimum admissible limit (VBATT<sub>MIN</sub>=3.2V)

- If VBATT>VBATT<sub>MAX</sub> at any time, the Wireless CPU may be damaged.

- If the transition time is too long, a high ripple of voltage may appear at the beginning of the burst transmission period; this high ripple may directly affect radio performance (phase error, modulation spectrum).

- Depends on the ripple frequency and amplitude, the RF performance may be affected (mainly the modulation spectrum).

### **3.5 Design Recommendation**

The key aspects of power supply design are:

- Quality of the power supply (impedance and transient).

- Supply track design between the power supply and the supply pins (VBATT) of the Wireless CPU.

- Decoupling capacitors.

### 3.5.1 Power Supply Selection

The power supply must have:

- A low output impedance

- A fast time response

- A good ripple rejection according to the Wireless CPU specification

- A capacity to deliver a high peak of current in a short time (2A)

There are different types of power supplies; some of these are not suitable for a GSM application because of noise generation, which may affect the RF performance.

### wavecom<sup>®</sup> confidential ©

Page: 24 / 90

Power Supply Recommendations

| Type of power supply                       | Power supply type and general behavior                                           | Recommendation                                                                                                                                                            |

|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linear Voltage regulator                   | Good regulation                                                                  | Recommended if<br>• Good ripple rejection<br>• Low drop of voltage<br>• Ability to deliver a high<br>peak of current (2A typ)                                             |

| Switching power supply with an embedded    | Except the switching frequency, which may affect                                 | Recommended if<br>• Good ripple rejection                                                                                                                                 |

| Pulse Width Modulation<br>system (PWM)     | the RF performance (mainly<br>the modulation spectrum),<br>the behavior is good. | <ul> <li>Low voltage drop</li> <li>Ability to deliver a high<br/>peak current (2A typ)</li> <li>If the switching frequency<br/>is not a multiple of<br/>100kHz</li> </ul> |

| Switching power supply<br>with an embedded | The constraint on the PFM is the switching frequency,                            | Avoid                                                                                                                                                                     |

| Pulse Frequency<br>Modulation system (PFM) | which varies according to the load.                                              |                                                                                                                                                                           |

|                                            | "The higher the sink current,<br>the higher the switching<br>frequency"          |                                                                                                                                                                           |

### **3.5.2 Design of the Supply Track**

To avoid any supply track related problems it is better to:

• Dedicate a track from the power supply output to the supply pins of the Wireless CPU.

-some other components connected to this track may also be sensitive to the voltage drop due to the Wireless CPU.

-other devices using the same power supply may generate noise

- Place the power supply output as close as possible to the supply pins of the Wireless CPU.

- Consider the output DC impedance of the power supply, DC impedance of the PCB layout, and the connectors and wires connecting the power supply to the Wireless CPU (forward and return path).

3.5.2.1 Voltage Drop and Impedance

The voltage drop may affect Wireless CPU performances if too high, but the maximum admissible voltage drop depends on its waveform. To guarantee the

### wavecom<sup>®</sup> confidential ©

Page: 25 / 90

Power Supply Recommendations

Wireless CPU performance, irrespective of the waveform, the voltage drop must stay within 300mV.

Under a 300mV maximum voltage drop with a current of 2A, the DC impedance of the tracks connecting the power supply output to the supply pin of the Wireless CPU may be as shown below:

### $300 \text{mV} / 2\text{A} = 150 \text{m}\Omega$ (return + forward path).

<u>Note:</u>

During a transmit burst, Wireless CPU nominal current is 1.4A only.

To design the Wireless CPU power supply track with a margin, <u>a target of 2A</u> is recommended.

Information on connector DC impedance and power supply DC output impedance is available in the datasheet.

In general, the constraints on the wires are:

- They are not shielded against radiated noise (TDMA noise, Digital noise)

- They do not support 2A current

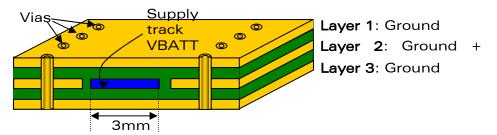

#### **3.5.2.2 PCB and Supply Track**

Designing a supply track on a PCB requires special care with a GSM application.

- The width of the track must be wide enough to decrease the voltage drop as far as possible

- The track must be surrounded by ground (through either  $\mu$ vias or a ground plane) to avoid coupled disturbances (Digital noise, RF noise)

In general, Wavecom recommends a supply track width>3mm as being sufficient.

### wavecom<sup>®</sup> confidential ©

Page: 26 / 90

Wireless CPU Q24 Series Power Supply Recommendations

## Caution:

The supply track must connect the 6 supply pins of the Wireless CPU:

- Pins 55, 57, 58, 59, and 60 for VBATT

- Pin 11 for VDD

If the ground track between the Wireless CPU and the power supply is a ground plane, it must:

- Not be parceled out

- Connect the four legs of the Wireless CPU.

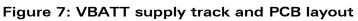

### **3.5.3 Decoupling capacitors**

Two decoupling capacitors (33pF and  $10\mu F$  with ceramic technology), close to the Wireless CPU supply pins are recommended.

The purpose is to avoid EMI/RFI EMI / RFI problems.

wavecom<sup>®</sup> confidential ©

Page: 27 / 90

Power Consumption

## **4 Power Consumption**

The Wireless CPU Q24 Series support different power consumption modes:

| Working modes         | Comments                                                                                        |

|-----------------------|-------------------------------------------------------------------------------------------------|

| ALARM mode            | The Wireless CPU is in OFF mode, when an ALARM occurs, the Wireless CPU wakes-up automatically. |

| FAST idle mode        | The Wireless CPU is synchronized with an RF GSM/GPRS network.                                   |

|                       | The internal 26 MHz of the Wireless CPU is constantly active.                                   |

| SLOW idle mode        | The Wireless CPU is synchronized with an RF GSM/GPRS tester.                                    |

|                       | The internal 26 MHz of the Wireless CPU is not constantly active.                               |

| FAST Standby<br>mode  | The SIM and Radio interface are deactivated via AT command or Open AT API:                      |

|                       | -The embedded open AT application is running,                                                   |

|                       | -The serial port remains active (AT commands are available).                                    |

|                       | The internal 26 MHz of the Wireless CPU is constantly active                                    |

| SLOW Standby          | This mode is similar to FAST Standby mode.                                                      |

| mode                  | All the features are disabled (no GSM, no GPRS, no SIM and no serial port)                      |

|                       | The internal 26 MHz of the Wireless CPU is not constantly active.                               |

| Communication<br>mode | A GSM/GPRS communication is established with an RF GSM/GPRS network.                            |

The power consumption depends on the configuration used.

To enable and find the measurement results given in the Product Technical Specification [3], it is recommended to follow the procedure described in the table below:

### <u>Note:</u>

Each power consumption mode may be enabled by using an AT command.

### wavecom<sup>®</sup> confidential ©

Page: 28 / 90

**Power Consumption**

| Working modes     | Measurement conditions                                                                                                                                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                 | Note                                                                                                                                                                              |

|                   | The settings which may change with the GSM/GPRS network are shown in blue                                                                                                         |

| ALARM mode        | AT+CALA="yy/mm/dd, hh:mm" is used to set an alarm and the Wireless CPU may be switched OFF using AT+CPOF.                                                                         |

|                   | Once the alarm has elapsed, the Wireless CPU starts automatically.                                                                                                                |

|                   | This method is used to save power when required.                                                                                                                                  |

|                   | -If the VBATT voltage is totally disconnected from the Wireless CPU, a back-up battery is needed to connect to the Wireless CPU.                                                  |

|                   | Notes:                                                                                                                                                                            |

|                   | -To set the time inside the module, the AT command<br>AT+CCLK="yy/mm/dd,hh:mm:ss" may be used                                                                                     |

|                   | -To check the time: AT+CCLK?                                                                                                                                                      |

|                   | -To avoid extra power consumption, when the Wireless CPU is in ALARM mode, do not apply any voltage in the UART1 interface.                                                       |

| FAST idle mode    | Paging every 9 multi-frames ( every 2 seconds)                                                                                                                                    |

|                   | Paging every 2 multi-frames ( every 0.5 seconds)                                                                                                                                  |

| SLOW idle<br>mode | AT+W32K=1 and the signal CT108-2/DTR1 must perform a rise edge (0V to 2V8).                                                                                                       |

|                   | Paging every 9 multi-frames ( every 2 Seconds)                                                                                                                                    |

|                   | Note: If the CT108-2/DTR1 signal perform a fall edge, the FAST idle mode is activated.                                                                                            |

|                   | AT+W32K=1 and the signal CT108-2/DTR1 must perform a rise edge (0V to 2.8V)                                                                                                       |

|                   | Paging every 2 multi-frames ( every 0.5 Seconds)                                                                                                                                  |

|                   | Note: If the CT108-2/DTR1 signal performs a fall edge, the FAST idle mode is activated                                                                                            |

| FAST Standby      | -The AT command "AT+WBHV=1, 1" is send to the Wireless CPU.                                                                                                                       |

| mode              | -The Wireless CPU is re-started in order to take this new behavior into account. During the reset, the Wireless CPU is initialized without the GSM stack or network registration. |

|                   | -Current consumption is measured after the Wireless CPU is re-started                                                                                                             |

|                   | Notes:                                                                                                                                                                            |

|                   | -To deactivate this mode, AT+WBHV=1, 0 must be used and the Wireless CPU must be re-started.                                                                                      |

|                   | -If any data is to be transmitted through the network, the RF must be activated first. The GSM/GPRS communication may then be made to send data.                                  |

## wavecom<sup>®</sup> confidential ©

Make it wireless

**Power Consumption**

| Working modes     | Measurement conditions                                                                                                                                                                              |                                                 |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

|                   | Note                                                                                                                                                                                                |                                                 |  |

|                   | The settings which may change with the GSM/GPRS network are shown in blue                                                                                                                           |                                                 |  |

| SLOW Standby mode | -The AT command "AT+WBHV=1, 2" is sent to the Wireless CPU and the signal CT108-2/DTR1 must perform a fall edge (0V to 2.8V).                                                                       |                                                 |  |

|                   | -The Wireless CPU is re-started in order to take this new setting into account. During the reset, the Wireless CPU is initialized without the GSM stack or network registration.                    |                                                 |  |

|                   | Note: To de-activate this mode, the CT108-2/DTR1 must perform a fall edge (2V8 to 0V), then, the AT command AT+WBHV=1, 0 must be sent and the Wireless CPU must be re-started (power-OFF or reset). |                                                 |  |

| Communication     | GSM mode                                                                                                                                                                                            | GSM850 @PCL5 and PCL19                          |  |

| mode              |                                                                                                                                                                                                     | GSM900 @PCL5 and PCL19                          |  |

|                   |                                                                                                                                                                                                     | DCS1800@PCL0 and PCL15                          |  |

|                   |                                                                                                                                                                                                     | PCS1900@PCL0 and PCL15                          |  |

|                   | GPRS Class 8<br><b>Note:</b> GPRS attachment with                                                                                                                                                   | GPRS850 1TX/4RX slot @Gamma 3 and Gamma 17      |  |

|                   | AT+CGATT=0,0 or for automatic<br>attachment AT+WGPRS=0,0                                                                                                                                            | GPRS900 1TX/4RX slot @ Gamma 3 and Gamma 17     |  |

|                   |                                                                                                                                                                                                     | GPRS1800 1TX/4RX slot @ Gamma 3<br>and Gamma 18 |  |

|                   |                                                                                                                                                                                                     | GPRS1900 1TX/4RX slot @ Gamma 3<br>and Gamma 18 |  |

|                   | GPRS Class 10<br><u>Note:</u> GPRS attachment with<br>AT+CGATT=0,0 or for automatic<br>attachment AT+WGPRS=0,0                                                                                      | GPRS850 2TX/4RX slot @ Gamma 3 and Gamma 17     |  |

|                   |                                                                                                                                                                                                     | GPRS900 2TX/3RX slot @ Gamma 3 and Gamma 17     |  |

|                   |                                                                                                                                                                                                     | GPRS1800 2TX/3RX slot @ Gamma 3<br>and Gamma 18 |  |

|                   |                                                                                                                                                                                                     | GPRS1900 2TX/3RX slot @ Gamma 3<br>and Gamma 18 |  |

wavecom<sup>®</sup> confidential ©

Wavecom<sup>®</sup> Make it wireless

Page: 30 / 90

## **5** Interfaces

Some of the Wireless CPU Q24 Series interface signals are multiplexed, in order to limit the total number of pins.

This architecture is more flexible, but imposes some restrictions.

### Example:

If the SPI bus and  $I^2C$  bus are multiplexed and if the SPI bus is used, the  $I^2C$  bus is not available.

## A Caution:

To power-ON the Wireless CPU Q24 Series correctly and to avoid damage, all external signals must be inactive when the Wireless CPU Q24 Series is OFF.

## 5.1 Digital I/O and Peripheral Implementation

All digital I/O comply with 3 volts CMOS.

For further information on the Digital I/O of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

To interface the Wireless CPU digital signals with other logics, the possibilities are as follows:

- 3.3 V logic: some serial resistors (more than  $11k\Omega$ ) may be added to the tracks,

- For higher voltage logics, a resistor bridge or a level shifter may be used.

### **5.2 Serial Interface**

For further information on the Serial interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

### Note:

The SPI or I<sup>2</sup>C bus interface of the Wireless CPU supports only a <u>master</u> mode, with the Wireless CPU being the master.

### 5.2.1 SPI Bus

The SPI bus includes:

- Pin 10: A CLK signal (SPI\_CLK)

- Pin 8: An input /Output signal (SPI\_IO)

- Pin 28: An activation signal (SPI\_EN)

These three signals comply with the SPI bus standard.

### <u>Note:</u>

By using another activation signal (pin 26, SPI\_AUX), it is possible to connect two devices using a SPI bus.

### wavecom<sup>®</sup> confidential ©

#### Page: **31** / **90**

## Wireless CPU Q24 Series Interfaces

### 5.2.2 I<sup>2</sup>C Bus

The I<sup>2</sup>C interface includes:

- Pin 10: A CLK signal (SCL)

- Pin 8: A DATA signal (SDA)

The two signals are multiplexed with the SPI bus. They comply with the  $\rm I^2C$  bus standard.

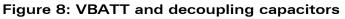

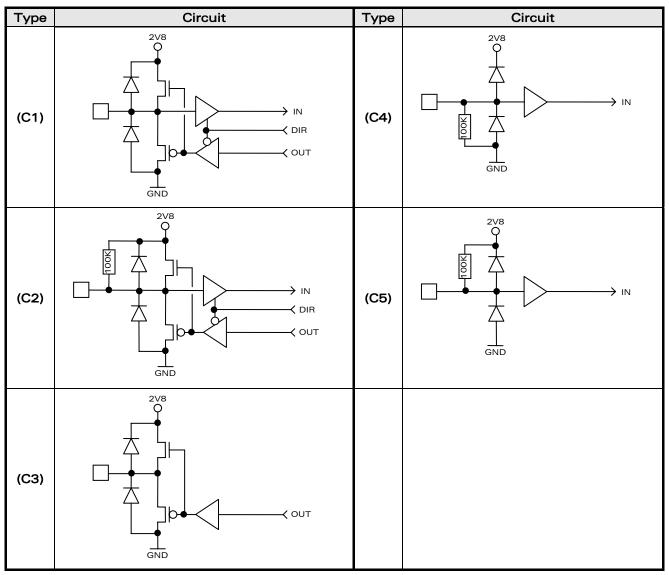

### **5.2.3 SPI and I<sup>2</sup>C Bus Implementation**

The SPI bus of the Wireless CPU Q24 Series is designed with three wires.

It is also possible to connect a device with a 4-wire SPI bus interface working in half or full duplex data rate by using external hardware.

The table below summarizes the possibilities:

wavecom<sup>®</sup> confidential ©

Page: 32 / 90

Interfaces

## wavecom<sup>®</sup> confidential ©

### Page: 33 / 90

## Wireless CPU Q24 Series Interfaces

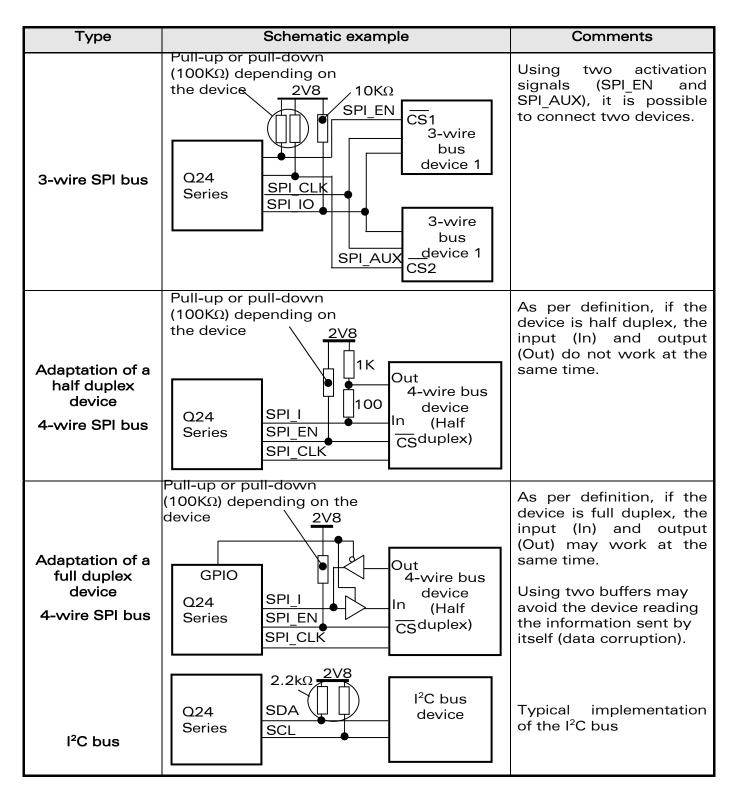

### **5.3 Keyboard Interface**

For a total of 25 keys (5 rows x 5 columns), the keyboard interface provides 10 connections:

- 5 rows (ROW0 to ROW4) and

- 5 columns (COL0 to COL4).

| Signals | Pin number | Description |

|---------|------------|-------------|

| ROWO    | 13         | Row scan    |

| ROW1    | 15         | Row scan    |

| ROW2    | 17         | Row scan    |

| ROW3    | 19         | Row scan    |

| ROW4    | 21         | Row scan    |

| COLO    | 23         | Column scan |

| COL1    | 25         | Column scan |

| COL2    | 27         | Column scan |

| COL3    | 29         | Column scan |

| COL4    | 31         | Column scan |

The scanning is digital, and the debouncing is performed in the Wireless CPU. No discrete components such as R, C (Resistor, Capacitor) are needed.

For further information on the keyboard interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

A typical implementation is as shown in Figure 9.

Figure 9: Example of Keyboard implementation

### wavecom<sup>®</sup> confidential ©

Page: 34 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

#### WM\_PRJ\_024NG\_CDG\_002-002

September 2006

### 5.4 Main Serial Link (UART1)

### 5.4.1 General Description

A flexible 6/8-wire serial interface is available complying with V24 protocol signaling, but not with V28 (electrical interface) due to a 2.8 volt interface.

The signals are:

- Pin 39: TX data (CT103/TXD1)

- Pin 32: RX data (CT104/RXD1)

- Pin 30: Request To Send (CT105/RTS1)

- Pin 37: Clear To Send (CT106/CTS1)

- Pin 36: Data Set Ready (CT107/DSR1)

- Pin 34: Data Terminal Ready (CT108-2/DTR1)

- Pin 51: Data Carrier Detect (CT109/DCD1).

- Pin 54: Ring Indicator (CT125/RI).

Figure 10: UART1 Serial Link signals

The UART1 serial interface allows a baud rate up to 460800.

For further information on the UART1 interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

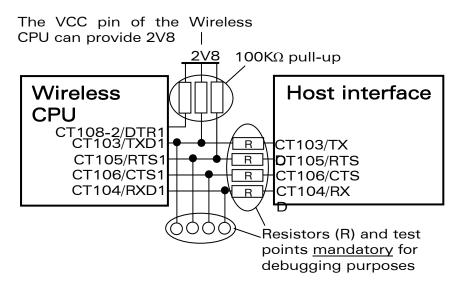

### 5.4.2 Design Recommendation

- To avoid extra power consumption or malfunction of the Wireless CPU, when the Wireless CPU is either in OFF mode or ALARM mode, do not apply any voltage to the UART1 signal.

- For download and debugging purposes, It is mandatory to have an access to the signals TXD1, RXD1, RTS1, and CTS1 (through test points for example).

- Because the signals DTR1, TXD1, and RTS1 are input pins of the Wireless CPU, irrespective of the application, it is mandatory to connect a pull-up on these signals (100kΩ to 2V8).

- Depending on the application, some serial link signals are not required:

- If the application manages only the audio, RXD1 and TXD1 signals are sufficient

### wavecom<sup>®</sup> confidential ©

Page: 35 / 90

#### Interfaces

- If the application manages some data transfer, it is mandatory to also use RTS1 and CTS1 (using RTS1 and CTS1 avoids data corruption).

- DSR1, DCD1, and RI may be left disconnected if not used; some applications, such as a modem, may require these signals.

## Examples:

#### 1-Typical implementation of the UART1 interface with a host interface

Figure 11: Typical UART1 and host connection

- When the Wireless CPU is in OFF mode, an over power consumption may occur if voltages are applied in the serial link.

- The rise and fall time of the reception signals (mainly TXD1) must be less than 200 ns:

High value serial resistors (R), placed in the serial link signals, may limit the current but, due to the input capacitance of the Wireless CPU (and host interface), if the value is too high, the maximum baud rate becomes limited.

wavecom<sup>®</sup> confidential ©

Page: 36 / 90

Interfaces

| UART1 baud | Host interface output voltage |                   |                  |  |

|------------|-------------------------------|-------------------|------------------|--|

| rate       | <3.1V                         | 3.2V              | 3.3V             |  |

| 9 600      | R < 62 kΩ                     | 6.8 kΩ< R < 62 kΩ | 11 kΩ< R < 62 kΩ |  |

| 19 200     | R < 30 kΩ                     | 6.8 kΩ< R < 30 kΩ | 11 kΩ< R < 30 kΩ |  |

| 38 400     | R < 15 kΩ                     | 6.8 kΩ< R < 15 kΩ | 11 kΩ< R < 15 kΩ |  |

| 57 600     | R < 10 kΩ                     | 6.8 kΩ< R < 10 kΩ | Not supported    |  |

| 115 200    | R < 5.1 kΩ                    | Not supported     | Not supported    |  |

The table below shows an example:

#### <u>Note:</u>

For a host interface output voltage of 3.1V, 3.2V or 3.3V, a typical value for the serial resistors is 4K7.

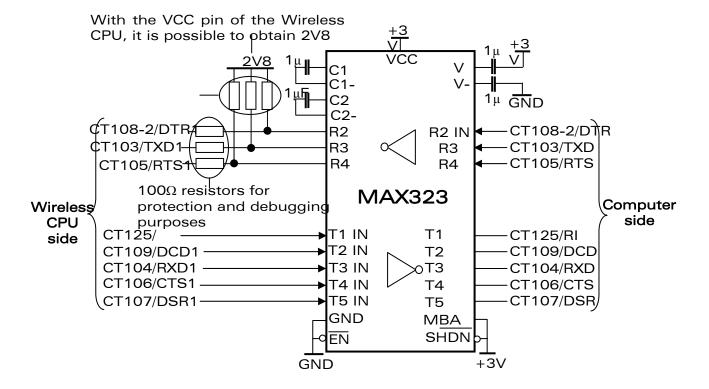

#### 2-Typical implementation of the UART1 interface with a terminal

To interface the UART1 with a terminal (a computer for example), a level shifter may be required.

In the example shown in Figure 12, a level shifter MAX3237E is used.

wavecom<sup>®</sup> confidential ©

Page: 37 / 90

Wireless CPU Q24 Series Interfaces

Figure 12: Example of RS232 level shifter implementation

## <u>Note:</u>

The MAX3238 is also compatible with the example shown in Figure 12.

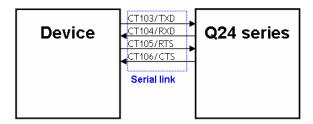

## 5.5 Auxiliary Serial Link (UART2)

#### 5.5.1 General Description

For specific applications, an auxiliary serial interface (UART2) is available on the Wireless CPU Q24 Series.

Example: Bluetooth connectivity.

For more information, see the AT Commands Interface Guide for Bluetooth [6].

## wavecom<sup>®</sup> confidential ©

Page: 38 / 90

Interfaces

#### Figure 13: UART2 Serial Link signals

For further information on the UART2 interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

#### 5.5.2 Design Recommendation

The design recommendations are the same as for UART1.

## **5.6 SIM Interface**

#### **5.6.1 General Description**

The following five signals are available:

- Pin 9: SIM power supply (SIM\_VCC)

- Pin 5: Reset (SIM\_RST)

- Pin 3: Clock (SIM\_CLK)

- Pin 7: I/O port (SIM DATA)

- Pin 50: SIM Card detection (SIM\_PRES)

The SIM interface can control a 1V8/3V SIM Card. This interface is fully compliant with the GSM 11.12 recommendations concerning SIM functions.

For further information on the SIM interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

#### Notes for SIM\_PRES connection:

- When not used, SIM\_PRES must be tied to 2V8 through a pull-up resistor

- When used, a rising edge means that the SIM Card is inserted whereas a falling edge means that the SIM Card is removed.

#### 5.6.2 Design Recommendation

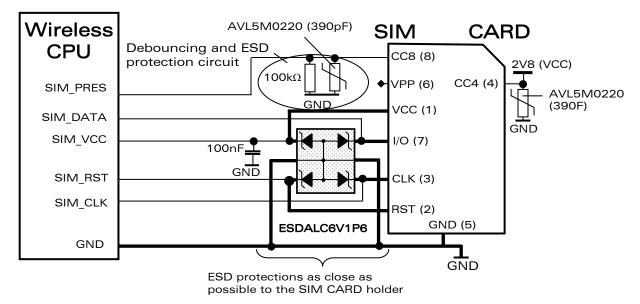

#### 5.6.2.1 ESD Protections

Low capacitance ESD protections (less than 10 pF) must be connected on SIM\_CLK and SIM\_DATA signals to avoid any disturbance of the rising and falling edges.

ESD protections are mandatory if the SIM holder is externally accessible. They must be placed as close as possible to the SIM socket.

## wavecom<sup>®</sup> confidential ©

Page: 39 / 90

#### Interfaces

The following references may be used: **ESDA-6V1P6** from ST Microelectronics and **AVL5M0220** from AMOTECH.

Figure 14: Example of SIM Socket implementation

## <u>Note:</u>

The capacitor in SIM\_VCC is placed to help the power to counteract spikes in the current consumption of the SIM up to the limits given in the compliance requirement, ensuring that the supply voltage stays in the specified range (Test Case 27.17.2.1.2).

The recommended value is 100nF.

#### 5.6.2.2 SIM CARD Holder

A good SIM CARD holder is one which:

- Prevents electrical disconnection of the SIM CARD

- Avoids direct ESD access to the pin of the SIM CARD holder (a shielded SIM CARD holder is more effective)

## wavecom<sup>®</sup> confidential ©

#### Page: 40 / 90

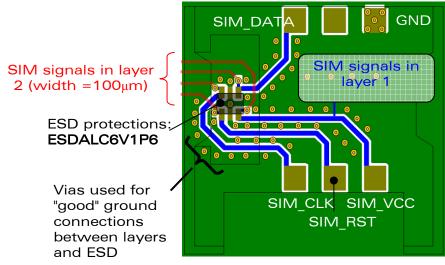

5.6.2.3 PCB Layout

Not only is the type of ESD protections important, but also their placement and connection.

ESD protections must be:

- As close as possible to the SIM CARD holder

- Connected to a "good" ground (important to dissipate the ESD energy)

- The track connections from the SIM CARD holder to the ESD protections must be as wide as possible (300  $\mu m$  minimum)

- It is recommended to decrease the length of the tracks between the Wireless CPU and the SIM connector **as much as** possible (<10 cm maximum).

Figure 15: Example of SIM Socket and PCB layout (Note: No SIM presence used)

## wavecom<sup>®</sup> confidential ©

Page: 41 / 90

Wireless CPU Q24 Series Interfaces

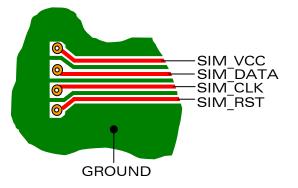

#### Note:

To avoid crosstalk, the SIM signals must be separated by a ground track:

Figure 16: SIM signals and layout

wavecom<sup>®</sup> confidential ©

Page: 42 / 90

Interfaces

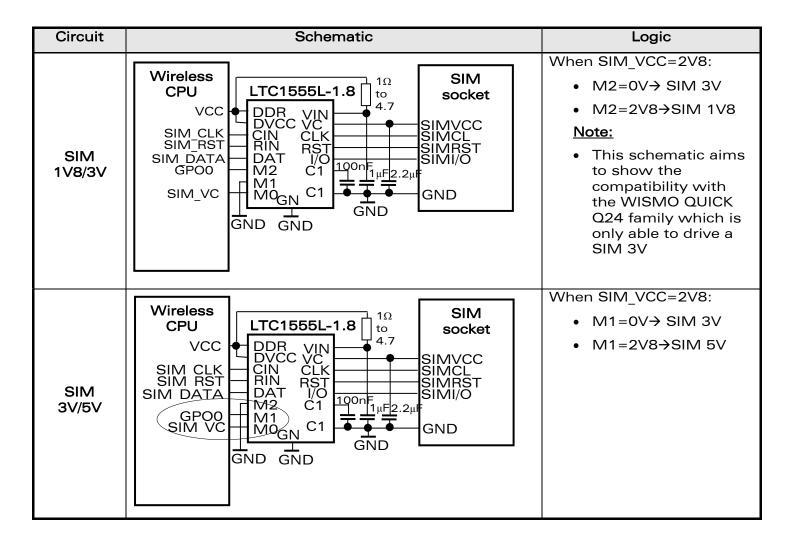

#### 5.6.2.4 SIM Management through an External Level Shifter

Like the WISMO QUICK Q24 family, the Wireless CPU Q24 Series is able to manage the 1V8/3V or 3V/5V SIM CARD by using an external voltage level shifter controlled by the GPO0 output signal (Pin 26).

The choice of an external level shifter device depends on the type of SIM. The Wireless CPU firmware triggers the GPO0 output signal (Pin 26), to automatically set the external SIM driver voltage level to match the voltage level of the SIM inserted.

With a voltage level shifter LTC1555L-1.8, the schematics are:

## wavecom<sup>®</sup> confidential ©

Page: 43 / 90

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

#### WM\_PRJ\_024NG\_CDG\_002-002

September 2006

Interfaces

## 5.6.3 Wireless CPU SIM CARD Holder

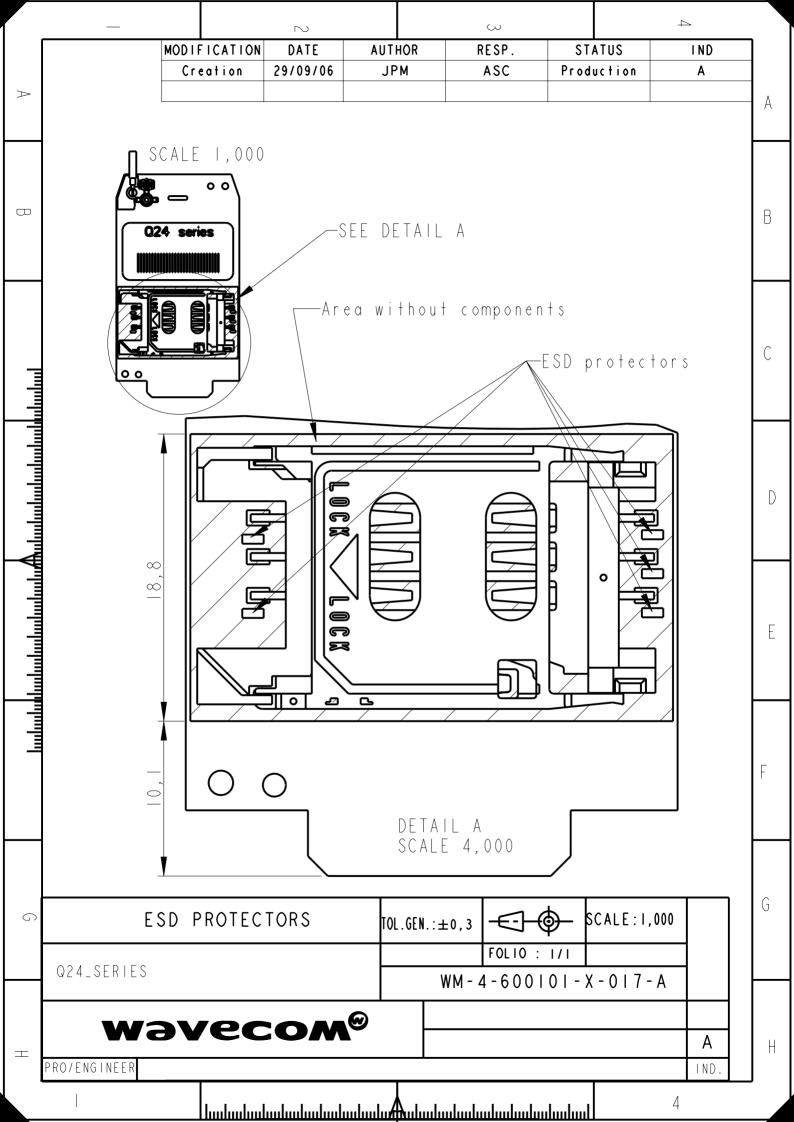

An optional SIM CARD holder may be used at the top of the Wireless CPU. This SIM CARD holder does not use the SIM\_PRES signal. Please refer to Figure 17: SIM CARD holder constraints on next page.

#### Figure 17: SIM CARD holder constraints (see next page)

A Wireless CPU equipped with a SIM CARD holder on top does not allow use of the SIM interface through the 60-pin GPC connector:

- The SIM interface through the 60-pin GPC connector needs to be not connected

- The SIM\_PRES signal of the Wireless CPU must be tied to VCC

wavecom<sup>®</sup> confidential ©

Page: 44 / 90

#### Interfaces

Environmental stress applied in the SIM CARD holder may interrupt or damage normal Wireless CPU operation.

The type of environmental stress may be:

• <u>ESD:</u>

- ESD protections (0402 package) close to the SIM CARD holder aims to decrease the effect of an ESD discharge on the SIM CARD holder.

- We recommend integration of such ESD protection when designing the mechanical aspects of the application.

- <u>Vibration:</u>

- A good mechanical design must prevent any direct contact with the SIM

- <u>Humidity</u>

A Caution:

Customers are advised to verify that the environmental specifications are compliant with the Wireless CPU Q24 Series.

The application must be qualified with the SIM Card in storage, transportation and operation.

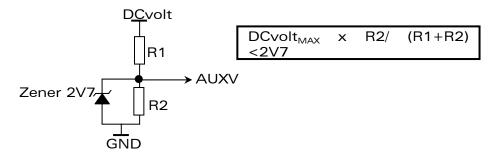

## **5.7 Analog to Digital Converter (ADC)**

Two Analog to Digital Converter are available on the Wireless CPU Q24 Series. These converters are 10-bit resolution, ranging from 0V to 2V8:

- Pin 33: AUXV0 (General Purpose Converter)

- Used to measure a voltage

- Pin 38: BAT\_TEMP (Battery Temperature monitoring or General Purpose Converter)

- If the Wireless CPU is supplied through a Li-Ion battery, the BAT\_TEMP input must be dedicated to the battery temperature measurement (see "Battery Charging Interface").

- If the Wireless CPU is not supplied by a Li-Ion battery, BAT\_TEMP may be used for another purpose similar to AUXV0.

For further information on the ADC interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

If AUXV0 and BAT\_TEMP are not used, they must be connected to ground.

## wavecom<sup>®</sup> confidential ©

Page: 46 / 90

Wireless CPU Q24 Series Interfaces

A typical application may be:

Figure 18: Example of ADC input implementation

## **5.8 Audio Interface**

Two different microphone inputs and two different speaker outputs are supported.

The Wireless CPU Q24 Series also include an echo cancellation feature, which allows hands-free operation.

## Caution:

- When speakers and microphones are exposed to the external environment, it is recommended to add ESD protection on the audio interface lines.

- It is important to select an appropriate microphone, speaker and filtering components to avoid TDMA noise.

For further information on the Audio interface of the Wireless CPU Q24 Series, refer to the Product Technical Specification [3].

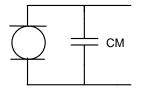

#### 5.8.1 Recommended Microphone Characteristics

- The impedance of the microphone must be around 2 k $\Omega$ .

- Sensitivity from -40dB to -50 dB.

- SNR > 50 dB.

- Frequency response compatible with the GSM specifications.

- To suppress TDMA noise, it is highly recommended to use microphones with two internal decoupling capacitors:

- CM1=56pF (0402 package) for the TDMA noise coming from the demodulation of the GSM 850 and GSM900 frequency signal.

- CM2=15pF (0402 package) for the TDMA noise coming from the demodulation of the DCS/PCS frequency signal.

## wavecom<sup>®</sup> confidential ©

Page: 47 / 90

Interfaces

These capacitors must be soldered in parallel to the microphone.

Figure 19: Microphone

#### 5.8.2 Recommended Speaker Characteristics

- Type of speakers: Electro-magnetic /10mW

- Impedance: 32 to  $150\Omega$ .

- Sensitivity: 110dB SPL min

- Receiver frequency response compatible with the GSM specifications.

#### **5.8.3 Recommended Filtering Components**

When designing a GSM application, it is important to select the <u>right</u> audio filtering components.

The strongest noise, called TDMA, is mainly due to the demodulation of the GSM850/GSM900/DCS1800 and PCS1900 signal: A burst being produced every 4.615ms; the frequency of the TDMA signal is equal to 216.7Hz plus harmonics.

The TDMA noise may be suppressed by filtering the RF signal using the right decoupling components.

The types of filtering components are:

- RF decoupling inductors

- RF decoupling capacitors

A good Chip S-Parameter simulator is proposed by Murata, and the following link may help to find it:

http://www.murata.com/designlib/mcsil.html

Using different Murata components, it is observed that the value, the package and the current rating may have different decoupling effects.

The table below shows some examples with different Murata components:

## wavecom<sup>®</sup> confidential ©

Page: 48 / 90

| Package       | 0402                |                                              |                                              |  |

|---------------|---------------------|----------------------------------------------|----------------------------------------------|--|

| Filtered band | GSM900              | GSM 850/900                                  | DCS/PCS                                      |  |

| Value         | 100nH               | 56pF                                         | 15pF                                         |  |

| Types         | Inductor            | Capacitor                                    | Capacitor                                    |  |

| Position      | Serial              | Shunt                                        | Shunt                                        |  |

| Manufacturer  | Murata              | Murata                                       | Murata                                       |  |

| Rated         | 150mA               | 50V                                          | 50V                                          |  |

| Reference     | LQG15HSR10J02       | GRM1555C1H560JZ01                            | GRM1555C1H150JZ01                            |  |

|               | or<br>LQG15HNR10J02 |                                              | or<br>GRM1555C1H150JB01                      |  |

| Package       | 0603                |                                              |                                              |  |

| Filtered band | GSM900              | GSM 850/900                                  | DCS/PCS                                      |  |

| Value         | 100nH               | 47pF                                         | 10pF                                         |  |

| Types         | Inductor            | Capacitor                                    | Capacitor                                    |  |

| Position      | Serial              | Shunt                                        | Shunt                                        |  |

| Manufacturer  | Murata              | Murata                                       | Murata                                       |  |

| Rated         | 300mA               | 50V                                          | 50V                                          |  |

| Reference     | LQG18HNR10J00       | GRM1885C1H470JA01<br>or<br>GRM1885C1H470JB01 | GRM1885C1H150JA01<br>or<br>GQM1885C1H150JB01 |  |

wavecom<sup>®</sup> confidential ©

wavecom<sup>6</sup>

Make it wireless

Page: 49 / 90

Interfaces

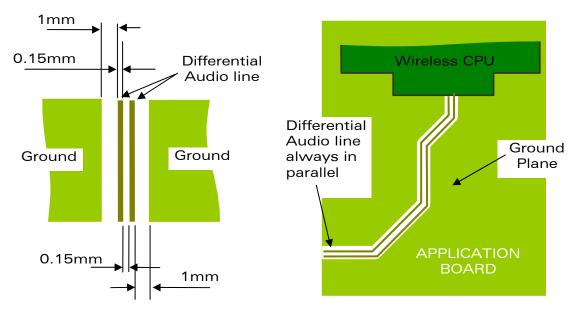

#### 5.8.4 Audio track and PCB Layout Recommendation

To avoid TDMA noise, it is recommended to surround the audio tracks by ground:

Figure 20: Audio track design

#### Note:

Avoid digital tracks crossing under and over the audio tracks.

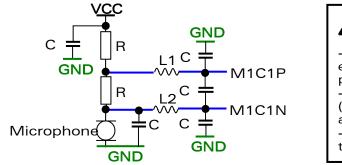

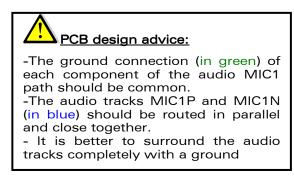

#### **5.8.5 Microphone Inputs**

The MIC1 inputs do not include an internal bias. MIC1/SPK1 may be used either for a hands-free system or a handset with external biasing circuit for the microphone.

The MIC2 inputs already include the biasing for an electret microphone, allowing easy connection to a headset.

#### 5.8.5.1 MIC1 Microphone Inputs